## Context Update of Aquila Interoperability Package (Aquila Lite) - Control Architecture and Philosophies

13th June 2024

Dong Chen

# Agenda

- Recap Context

- Control Architecture

- Specifications to de-risk control interactions

- Demonstration of generic model co-simulated with GE supplied model

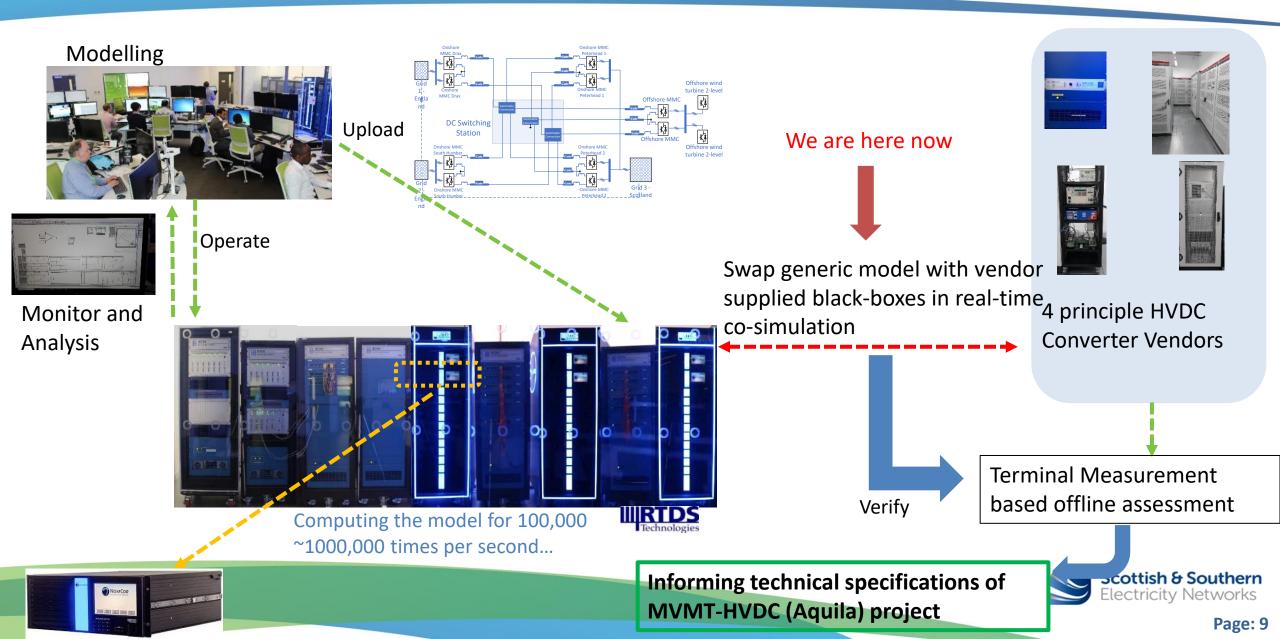

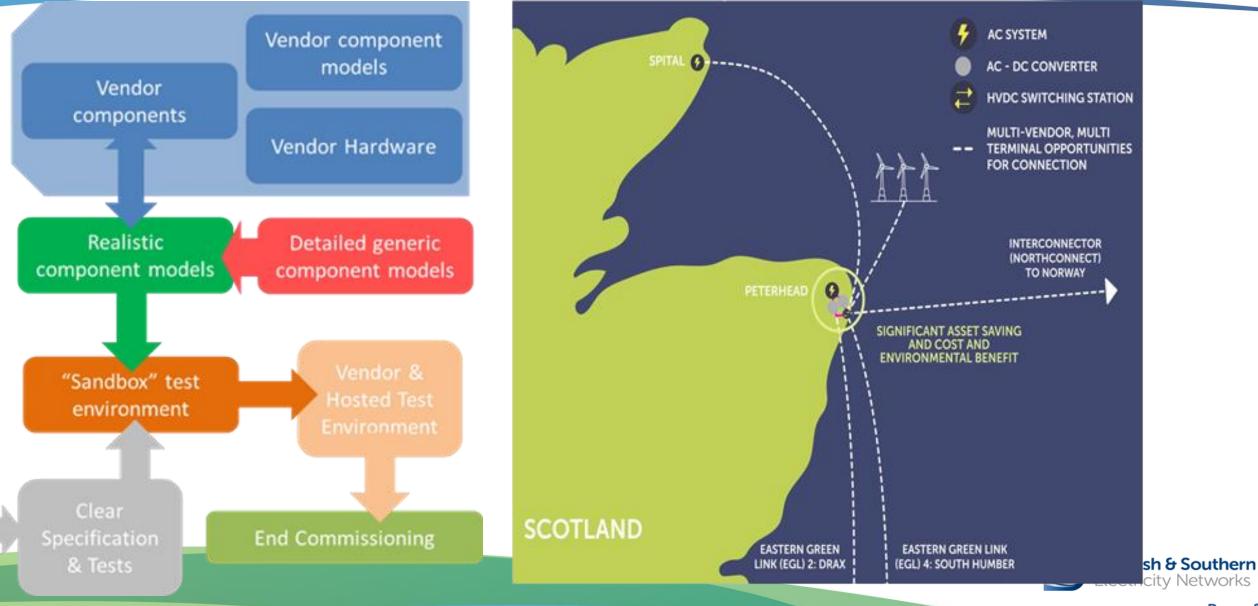

# Flow Chart before Commissioning Project Aquia The National

# Benchmark System

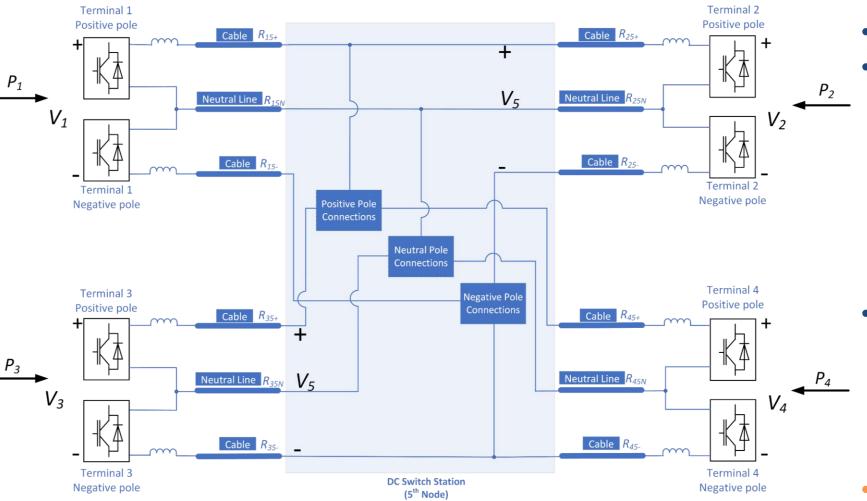

- Radial Network

- Earthing assumptions:

- Full bipolar terminals unearthed

- DCSS earthed via low resistance

- Rigid bipolar terminals earthed via low resistance

- In simulation, the differences between rigid and full bipolar sections are represented by different impedance values of neutral lines

- Control power driven by AC dynamics is future work Scottish & Southern

Page: 4

Networks

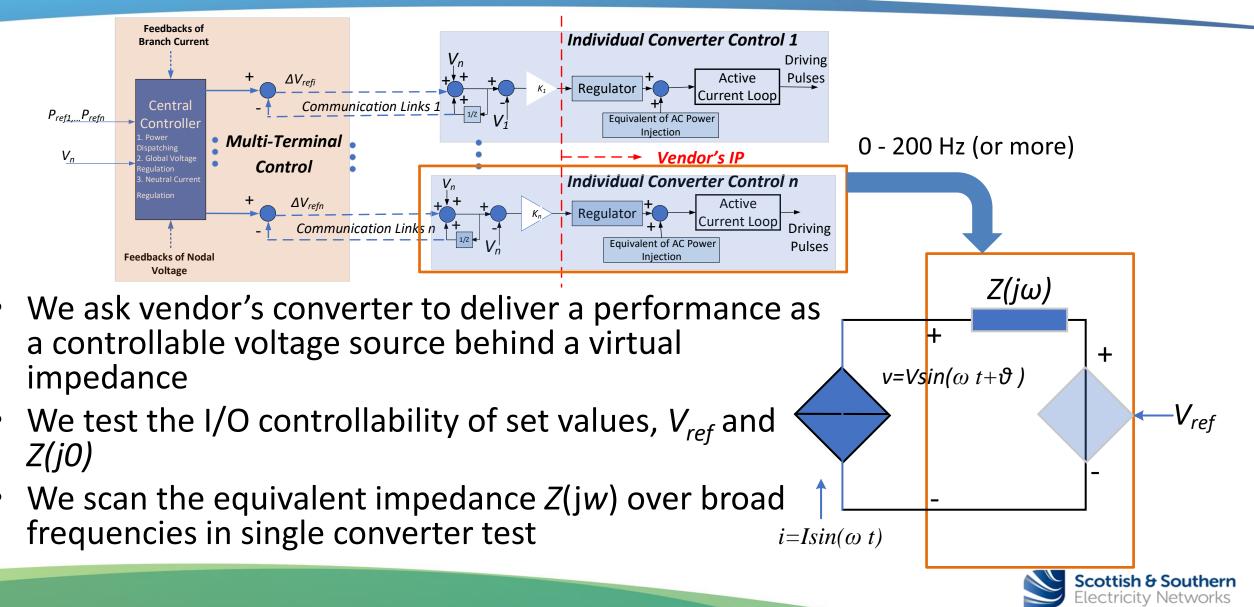

#### MVMT-HVDC Steady State Control Architecture

- Defining the interfaces of primary control and electrical connection in a vendor agnostic manner

- performance defined by TSO

- delivered by vendor

- Secondary control cascaded to the inputs of primary control orders

- Designed By TSO (HVDC Centre)

- delivered by vendor

- ✓ Power control

- ✓ DC voltage bias control

- ✓ Neutral Current Control

- MIMO optimization functions in future work

### What to specify and what to test?

Methodologies to Quantify MVMT-HVDC stability 🔘

#### -1.Security domain of power flow

- "CX-Index" as a global scaler index

- How "far" an operating point is from the completion of no-load energization

- 2. Small-signal MIMO non-minimum-phase stability over broad frequencies

- Interaction stability

- Transfer stability

- Local stability

-Additional one: robustness against measurement error

Page: 7

The National

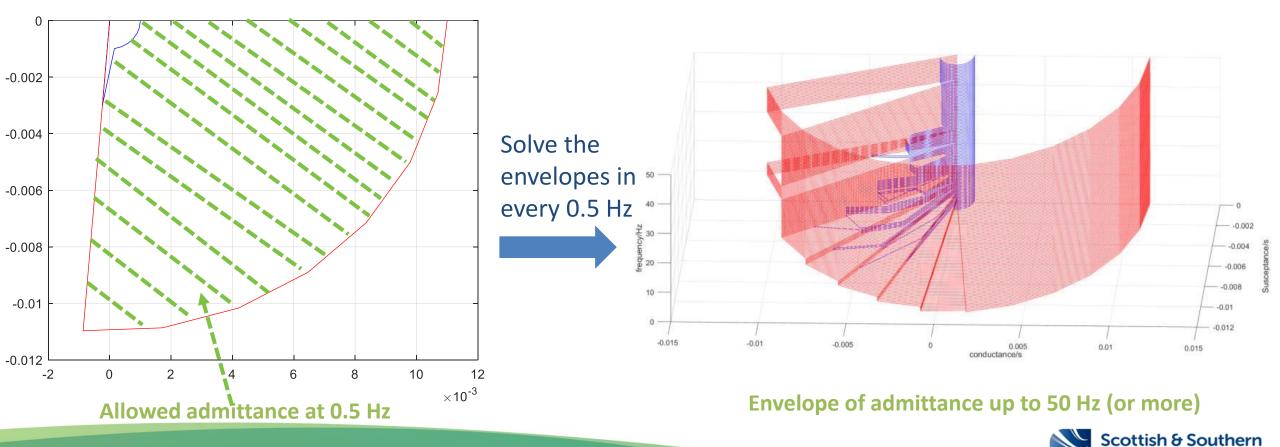

# Dummy Specifications for Interaction Stability (

- Envelopes of frequency-dependent admittance (I/V) of converter

- Solver Input: Network Impedance  $\rightarrow$  Solve Output: Envelopes of Converter Impedance

The National

Centre

### **MVMT-HVDC** Test Scheme